在深圳前海深港青年梦工场,有一条名为“5th RISC”的“路”。这是由睿思芯科(深圳)技术有限公司设置的装饰路牌。

在计算机界,“RISC”可谓大名鼎鼎,基于其建立的免费、开放的指令集架构RISC-V的开源模式,能大幅降低芯片设计的周期和成本。2月11日,由市委宣传部组织的“高质量发展调研行之走进深圳人工智能企业”采访活动走进睿思芯科,探访这位“芯片先锋”。

剪辑:王晓林

等待最满意的“鹦鹉芯片”

从“5th RISC”路牌出发,往前几步就到了睿思芯科。走进公司,三幅鹦鹉的卡通图引人注目。公司创始人、CEO谭章熹表示,每一幅图都对应着公司自主研发的一款芯片。不仅如此,公司的logo也是一只鹦鹉。“我曾经不小心把自己养的宠物鹦鹉弄丢了,所以有种特别的情怀。等以后研发出最满意的芯片,我要用那只鹦鹉的名字来命名。”他介绍道。

睿思芯科以鹦鹉的名字为公司推出的每一款芯片命名并附上卡通图片。

如此感性思维的谭章熹,是理工科博士出身。

师从2017年图灵奖得主、RISC-V指令架构开创者David Patterson教授,谭章熹是RISC-V原创项目组核心成员之一。在加州大学伯克利分校读博期间,他深度参与了RISC-V的孵化成长过程。

据悉,第五代精简指令集(RISC-V)是一种基于精简指令集计算(RISC)原理建立的开放指令集架构,由美国加州大学伯克利分校研究团队于 2010 年设计。凭借开源、架构简单、模块化等优势,RISC-V迅速崛起,打破了X86和Arm架构的双寡头格局。众多小公司和初创企业借助RISC-V指令集大幅降低芯片设计的周期和成本。伴随物联网、5G 通信等技术的兴起,为 RISC-V落地应用打开了广阔的新空间。

“要做真正有影响力的事,还得自己创业。”意识到这一点,2018年,谭章熹回国并在深圳成立了睿思芯科,这也是中国最早做RISC-V指令集芯片的公司之一。成立之初,这个年轻团队一度面临从零开始的难题,从技术、人才到市场,都得靠自己摸索。

谭章熹表示,选择深圳不是偶然。在他看来,深圳所在的大湾区的创新资源与硅谷十分接近。睿思芯科当初要在香港设立子公司,需办理境外直接投资(ODI)备案,这个申办过程在别的地方需要三到九个月,但在前海20天就批了下来。

如此高效的创新热土,给了团队极大信心。经过7年耕耘,如今公司已研发出多款高能效、高性能的处理器产品,并与世界500强中的多家芯片核心头部厂商合作落地,为其提供IP授权和SoC定制化开发合作。

睿思芯科推出的一款芯片对应的卡通图

每年推出一款自研芯片

今年除夕夜,谭章熹和核心研发团队在楼下吃了顿年夜饭,便赶回公司继续讨论芯片的点亮,不知不觉到了凌晨一点多。“做半导体很辛苦”,刚入行时他便有了这个清醒认知。在国外曾与多位顶级科学家共事,他发现自己见过的最聪明的人,同时也是最努力的。

“无论做什么,最重要的是找到自己的passion所在。”在这个信念的激励下,怀着对半导体行业的极大热情,谭章熹几年如一日地在创新上下功夫。如今,公司保持着每年推出一款芯片的节奏,这样的节奏对初创公司来说已属难得。

“每一行代码都是在中国,由中国工程师敲出来的。”睿思芯科的宣传册上有这么一句话。

“算力这个赛道很热闹,供应链上的风险很大,新质生产力的架构创新迫在眉睫。”谭章熹介绍,经过多年的发展,睿思芯科在RISC-V架构的高性能处理器领域取得了多项突破性成果。尤其在RISC-V架构的高性能处理器研发、芯片互联技术及服务器级CPU设计方面形成了独特的竞争优势。

据统计,睿思芯科在芯片互联领域布局了多项专利,拥有37项RISC-V领域发明专利,涵盖超标量向量融合架构、异构互联技术、动态功耗管理等核心领域。

目前,睿思芯科正在推进服务器级CPU研发。通过从指令集、编译器到芯片封装的软硬件全栈自主化,打造全国首个完全基于RISC-V的高性能服务器芯片生态闭环。与此同时,睿思芯科还借鉴软件开发中的开源理念,将其引入硬件开发中,开创了硬件开发的迭代模式。

2024年,睿思芯科荣获国家级专精特新“小巨人”企业称号。

编辑 刘悦凌 审读 郭建华 二审 李怡天 三审 刘思敏

读特热榜

读特热榜

IN视频

IN视频

鹏友圈

鹏友圈

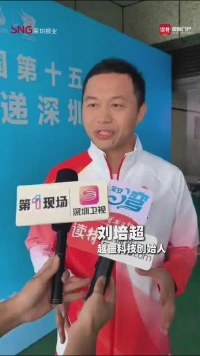

11月9日,我们将迎来第十五届全国运动会(以下简称“十五运”)。赛事临近,无论你是投身运动热潮、感受竞技魅力,还是想为拼搏健儿传递心意,都不妨来鹏友圈,留下对“十五运”的专属祝福!带上话题#我为十五运加油#,一同为运动健儿呐喊助威,为“十五运”热烈喝彩! 【本期话题】#我为十五运加油# 【活动礼品】读特积分、优质动态随机掉落深圳盒子 【活动时间】即日起至11月22日

第十五届全国运动会已进入冲刺倒计时,想解锁超省心的观赛方式?赶紧打开“十五运全景魔方”(https://huodong.dutenews.com/H5/nationalGame/pc),一键解锁观赛全攻略!无论是赛事速递、赛程全览,还是购票指南、规则科普,都能在这里轻松找到!快到鹏友圈带话题晒出你的使用截图,和鹏友们分享专属观赛攻略吧! 【本期话题】#十五运观赛神器# 【活动礼品】读特积分、优质动态随机掉落深圳盒子 【活动时间】即日起至11月22日

01:00

01:00#十五运读特小记者推荐官# 深圳,创新之城,活力之都,邀您共赴十五运之约 深圳,这座改革开放的先锋城市,以创新为魂,活力为韵,正张开双臂欢迎四方来客。在这里,高楼林立,平安金融中心直插云霄,深圳湾“春笋”展现滨海艺术魅力,市民中心如大鹏展翅,彰显行政心脏的活力。 深圳还是“千园之城”,1320座公园如绿色明珠镶嵌城市,大鹏半岛的碧海银沙与梧桐山的云海日出,让人流连忘返。漫步南头古城,千年文脉与现代文创交织;走进大芬油画村,艺术气息扑面而来。 十五运会期间,深圳更添独特魅力。在宝安欢乐剧场等智能场馆,AR导航、AI机器人服务等前沿科技,让您体验未来之城的精彩。赛事之余,您可参与“全民全运”系列活动,在虹桥公园自由式小轮车赛场感受激情,在深圳湾畔的马拉松赛道尽览山海美景。 十一月的深圳,阳光与激情同在。让我们相约深圳,在十五运的青春礼花中,共赴一场创新与活力的盛宴!

01:11

01:11#十五运读特小记者推荐官# 亲爱的全国各地朋友们: 如果让我用一个词形容我的城市,那一定是“奔跑”。深圳,就像我们班那个永远充满奇思妙想的同学,永远在创造,永远向前。 站在莲花山顶俯瞰,你会看见这座城市的心跳——高楼如雨后春笋般生长,深南大道上车流如织。但深圳的魅力不止于此。周末的深圳湾,白鹭在红树林上空划出弧线,远处香港的青山若隐若现。科技园的深夜,大厦里依然亮着点点灯光,那是无数梦想在发光。 这里是大疆无人机起飞的地方,是腾讯QQ诞生的摇篮。走在华侨城创意园,旧厂房变身艺术空间,咖啡香混着油墨味;盐田港的巨轮鸣着汽笛,把“中国制造”送往世界每个角落。 来自天南地北的人,带着各自的乡音和梦想,把这里变成了家的模样。 朋友们,欢迎你们来看看这座“奇迹之城”。来感受创新的脉搏,看看科技与自然如何共舞,体会什么是“时间就是金钱,效率就是生命”。这座城市,会用它年轻的心跳告诉你:梦想,永远值得奔跑。 深圳准备好了,期待与你相遇!

【十月再见,十一月你好】 金秋十月,我们度过了欢乐的国庆和团圆的中秋佳节…初冬十一月,十五运会来啦🏃♂️“激情全运会,活力大湾区”,深圳准备好了!莲花山簕杜鹃花展🌺 (11.7-11.21)也安排上了!让我们一起加油,迎接十一月的活力与美好,坚持热爱,奔赴下一场山海,拥抱十一月的精彩#我为十五运加油#

- 友情链接: 深圳新闻网

- 粤ICP备10228864号

- 粤公网安备 44030402000917号

- Copyright @1997-2023 深圳特区报社